جدید گیت منطقی And

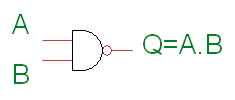

همان طور که از نام این گیت مشخص است، خروجی آن فقط زمانی صحیح یا True یا High یا 1 منطقی خواهد بود که دو ورودی هر دو True باشند. نماد شماتیک گیت AND به شکل زیر است:

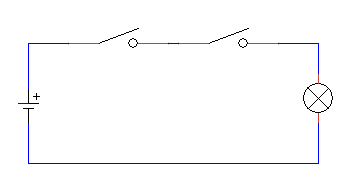

و عملکرد آن را به طریق ساده می توان با این شکل نشان داد:

برای تحلیل این گیت مانند گیت NOT فرض می کنیم که ولتاژ +5 معادل مقدار منطقی 1 یا همان صحیح یا True و ولتاژ 0 معادل مقدار منطقی 0 یا False است.

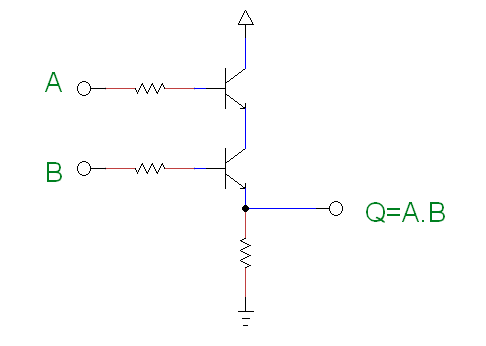

یک مدار ترانزیستوری که عملکرد گیت AND را شبیه سازی می کند در شکل زیر نمایش داده شده است.

کاملا واضح است که اگر ولتاژ هر یک از مقادیر ورودی A و B تقریبا برابر 0 ولت یا در واقع همان Low یا False نباشند ترانزیستور متناظر در حالت قطع قرار گرفته و ولتاژ خروجی Q برابر 0 خواهد بود که همان 0 منطقی است. بنابراین تنها زمانی می توانیم انتظار خروجی High داشته باشیم که هر دو ترانزیستور در حالت اشباع قرار گیرند و این تنها در صورتی امکان پذیر است که هر دو ورودی به طور هم زمان High باشند.

با بسط همین تحلیل می توان دریافت که عمل AND بر روی هر تعداد ورودی تنها زمانی منجر به خروجی True خواهد شد که همه ورودی ها True باشند و تنها False شدن یکی از آنها باعث خواهد شد که خروجی نیز False شود.

آی سی های TTL گیت AND عبارتند از 7408 ، 7811 ، 7421 و آی سی های CMOS مشتمل است بر CD4081 ، CD4073 و CD4082.